**ISSN (Online) 2394-6849**

## International Journal of Engineering Research in Electronics and Communication **Engineering (IJERECE)** Vol 4, Issue 3, March 2017

# High-Speed, Low Area and Energy Efficient 32bit Carry Skip Adder using verilog HDL

<sup>[1]</sup> Konduru Lakshmi Bhanu Prakash Reddy, <sup>[2]</sup> Dr.S.Vijaya Kumar <sup>[1]</sup> PG Scholar <sup>[2]</sup> Associate Professor. <sup>[1][2]</sup>Dept.of ECE Sreenivasa Institute of Technology and Management Studies Chittoor A.P, INDIA

Abstract: -- Adders are basic essential component used in DSPs Processors and Digital filters and widely used in the Digital Integrated Circuits and also in Analog ICs.In this paper, a carry skip adder structure that has a higher speed, Low area as well as lower energy consumption compared with other adders is presented. The speed and reduction in the design area can be achieved by using "HYBRID MUX" instead of conventional MUX for skip logic in the existing method. In addition, instead of utilizing compound gates (AOI&OAI), the proposed structure makes use of "HYBRID MUX" for the skip logic. The Proposed structure assessed by comparing their speed, delay, area & energy parameters with those of other adders using a 45-nm static CMOS technology. The results that are obtained by Xilinx tool. Simulation reveals, on average 45% and 40% improvements in the delay &energy, respectively compared with conventional one. The power delay product is the lowest among all adders.

Keywords:-- Hybrid Mux, cska, nmos pmos, xor gate, high speed, low area

## I. INTRODUCTION

The increasing demand for mobile electronic devices requires use of power efficient, low area and high speed in VLSI Circuits. Addition is the most arithmetic operation and addition plays an important role in processors, Filter designs and DSP Applications.

Adders are a main building block in ALUs [1] and hence reducing their power consumption and increasing their speed mainly affect the speed, area and power consumption of DSPs, Filters and processors. There are different methods on the subject of minimizing the power and speed of these units, which have been discussed in [2]-[9]. Truly, it is highly desirable to achieve higher speeds at low energy/power consumptions, which is a challenge for the designers of VLSI circuits.

One of the main techniques to lower the energy/power consumption of digital circuits is to reduce the supply voltage due to quadratic dependence of the switching energy on the voltage. A Complex DSP system contains many adders. The Designers are forced with more constraints are high speed, high throughput, small silicon area and low power consumption. Many design styles of adders exist in VLSI. Although, Ripple carry adders are the small in design structure but it's very slower. Recently, carry-skip adders are used popularly due to their performance of high speed and small size. There are many different adder families with different power consumptions, delays and area usages. The examples include RCA, CIA, CSKA, CSLA and PPAs may be found in [1] and [13].

The CSKA, which is an effective adder in terms of area usage, power consumption, was discussed in [17]. The critical path delay of the CSKA is much smaller than the RCA, but the power consumption and its area usage is similar to RCA. The power delay of the CSKA is smaller than that of the PPAs and CSLAs. In addition to this, due to small number of transistors, the CSKA benefits from the wiring lengths. The CSKA structure, on reducing its delay by using static CMOS Logic. The proposed method increases the speed considerably while maintaining the low power consumption and area properties of CSKA. Hence, the contribution of this paper can be summarized as follows.

1) Proposing a modified CSKA structure by using HYBRID MUX instead of conventional multiplexer and compound gates in the existing once. The rest of the paper is ordered as follows. Section II describes about the existing methods and section III describes about the proposed method. Section IV shows the simulation Results. Finally, the Conclusion is drawn in section V.

#### **II.EXISTING METHODS**

Conventional carry skip adder (existing method 1): The block diagram of an M-bit Conv. CSKA,

contains the blocks of the RCA, is as shown in the Figure 1.In addition to the Chain of FULL ADDERs in each stage, there is a carry skip Logic.

Figure 1. Conventional Carry Skip Adder

An RCA Contains M cascaded FULL ADDERS, the worst propagation delay of the addition of two M-bit numbers, A and B, belongs to where all the FULL ADDERS are in propagation mode. The CARRY SKIP operation can be performed by the multiplexers as shown in the above figure.

To design this conv.multiplexer 12 transistors are required. So propagation delay and also area of the design also increases. To reduce the propagation delay one may use the compound gates for the SKIP Logic. The Power consumption of the compound gates (AOI and OAI) smaller than that of multiplexer but the power consumption of the CI-CSKA (EXISTING METHOD 2) is more than that of CONV. CSKA.

#### CI-CSKA Existing Method :

The block diagram is based on combining the concatenation and incrementation methods with the Cons-CSKA block diagram, and hence it is denoted by CI-CSKA. In this the skip logic replaced by compound gates and the sum can be produced from the incrementation blocks. The incrementation blocks contains xor gates and and gates (HALF ADDERS). The CI-CSKA as shown in the below Figure 2.

Figure 2.CI-CSKA

Due to this incrementation blocks area of the design increases and propagation delay also increases. In this adder the designer may give zero the carry input signal for the each RCA block as shown in above figure. On each consequent stage the is complemented and also one NOT gate is used to compliment the carry. It increases the delay area and power but speed of the operation is highest. But the SKIP LOGIC (AOI or OAI compound gates) is not able to bypass the zero carry input until the zero carry input propagates from the corresponding RCA block. To solve this problem, in the proposed method the SKIP logic can be implemented by using "HYBRID MUX".The details of proposed method is discussed in the following section.

## **III.PROPOSED METHOD**

#### **Proposed Hybrid CSKA:**

In the proposed method the Skip logic can be implemented by "HYBRID MUX" instead of conv. Mux and also compound gates. By using this hybrid mux speed of the operation increases, power consumption decreases and also the design area reduces. The proposed method of CSKA as shown in below Figure 3.

Figure 3. Proposed Hybrid CSKA

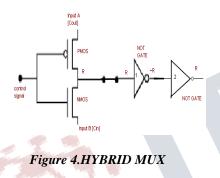

#### HYBRID MUX:

Hybrid mux is similar to the CMOS Inverter. The hybrid mux consists of one NMOS, one PMOS and two NOT gates. The structure of hybrid mux as shown in below Figure 4.It contains two inputs and one output and one conditional signal. The hybrid mux having one NMOS, one PMOS followed by two NOT gates as shown in the Figure

4.To design the hybrid mux 12 transistors are required. The conditional signal is generated by the partial products of the input bits. All these partial products are applied to an AND gate to generate the conditional signal. If the conditional signal is equal to one NMOS transistor is ON and PMOS transistor is OFF. The NMOS is connected to the Cin and PMOS is connected to the Cout of the RCA block. If NMOS is ON the input carry signal is directly connected to the next stage. If the conditional signal is equal to the "zero" PMOS transistor is ON and NMOS transistor is OFF. The Cout of the RCA block can acts as a carry signal for next stage. It reduces the propagation delay of the carry, and also reduces the design area.

**IV. SIMULATION RESULTS**

In this the simulation results are obtained by using the Xilinx tool. The coding of the design is written in verilog HDL Language and Simulated. The Simulation is analyzed in Xilinx 12.1.The simulation results as shown in the Figure 5.Here the Table 1 shows the comparison of No. Of LUTs, Power consumption, delay and No. Of IOB's of the CONV CSKA, CI-CSKA, MODIFIDE CSKA and HYBRID CSKA.

| Chjerk ↔        | T P X    | J.  |            |       | 5 0CC000 08                                                                                                                                                 |

|-----------------|----------|-----|------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Simulation Obj  | jects fo | æ   |            |       |                                                                                                                                                             |

| TIN)            | 16 »     | 8   | ne         | Va    | Ous  2us  4us  6u                                                                                                                                           |

|                 |          | 1   | 👸 a [31:0] | ZZ    | 22222                                                                                                                                                       |

| ct Name         | Valu     | P   | 6 b[01:0]  | 223   | ZZZZZ                                                                                                                                                       |

| a[31:0]         | 000      | 0   | la cin     | z     |                                                                                                                                                             |

| b[31:0]         | 000      | ñ   | s[E1:0]    | XX3   | 30000 11111 01010 XIIIII. 11111 X00000                                                                                                                      |

| cin<br>sD1:0    | 1 000    | ×.  | La cout    | x     |                                                                                                                                                             |

| ( ccut          | 010      | 1   | (E2.1)     | XZ    | 77777                                                                                                                                                       |

| (D2:1)          | 024      | 4   |            |       |                                                                                                                                                             |

| x[4:1]          | 000      | ł   | (k 1       | хxо   |                                                                                                                                                             |

| p[31:0]         | 050      | 1.  | g p[31:0]  | XX    | <u>&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;&gt;</u> |

| y[3:1]          | 101      | Ľ,  | 👷 y[11]    | XX)   | XXX 000 111 X 101                                                                                                                                           |

| ) q[4:1]        | 010      | ŤI. |            |       |                                                                                                                                                             |

| ) <b>(</b> 4:1] | 101      |     | /          | cska3 | 2/y[31])00000 us                                                                                                                                            |

|                 |          |     |            |       |                                                                                                                                                             |

Figure 5. Simulation Results

## **DESIGN SUMMARY:**

| cska32 Project Status (02/17/2017 - 14:05:53) |                                 |                       |                        |  |

|-----------------------------------------------|---------------------------------|-----------------------|------------------------|--|

| Project File:                                 | lakshmi703.xise                 | Parser Errors:        | <u>0 Errors</u>        |  |

| Module Name:                                  | cska32                          | Implementation State: | Synthesized            |  |

| Target Device:                                | xc3s500e-4fg320                 | •Errors:              | <u>OErrors (O new)</u> |  |

| Product Version:                              | ISE 12.1                        | •Warnings:            | No Warnings            |  |

| Design Goal:                                  | Balanced                        | Routing Results:      |                        |  |

| Design Strategy:                              | <u>Xîinx Default (unlocked)</u> | • Timing Constraints: |                        |  |

| Environment:                                  | System Settings                 | Final Timing Score:   |                        |  |

|                               |             |                          | Maximize         |                          |                        |

|-------------------------------|-------------|--------------------------|------------------|--------------------------|------------------------|

| Detailed Reports              |             |                          |                  |                          |                        |

| Report Name                   | Status      | Generated                | Errors           | Warnings                 | Infos                  |

| Synthesis Report              | Current     | Fri Feb 17 14:10:20 2017 | 0 Errors (0 new) | 0                        | 0                      |

| Translation Report            | Out of Date | Mon Dec 5 15:28:57 2016  | 0                | 0                        | 0                      |

| Map Report                    | Out of Date | Mon Dec 5 15:29:02 2016  | 0                | 0                        | <u>2 Infos (0 new)</u> |

| Place and Route Report        | Out of Date | Mon Dec 5 15:29:18 2016  | 0                | 0                        | <u>1 Info (0 new)</u>  |

| Power Report                  | Out of Date | Mon Dec 5 15:08:11 2016  | 0                | <u>1 Warning (0 new)</u> | <u>1 Info (0 new)</u>  |

| Post-PAR Static Timing Report | Out of Date | Mon Jan 30 15:50:54 2017 |                  |                          |                        |

| Bitgen Report                 |             |                          |                  |                          |                        |

Maximira

Partition Implementation Status

-----

No Partitions were found in this design.

-----

Generating "PAR" statistics.

Timing Score: 0 (Setup: 0, Hold: 0)

Generating Pad Report.

All signals are completely routed.

Total REAL time to PAR completion: 14 secs Total CPU time to PAR completion: 13 secs

Peak Memory Usage: 188 MB

| TABLE  | 1:-Com  | narison | of different | CSKA  |

|--------|---------|---------|--------------|-------|

| Indull | 1. 0000 | parison | oj aljjerent | COLLI |

| LOGIC Utilization         | CONV<br>CSKA              | CI-<br>CSKA                  | MODIFIDE<br>CSKA          | HYBRID<br>CSKA            |

|---------------------------|---------------------------|------------------------------|---------------------------|---------------------------|

| No. of LUTs               | 72 Out<br>of<br>9312      | 75<br>Out of<br>9312         | 68 Out of<br>9312         | 57 Out of<br>9312         |

| No. of bonded IOB s       | 98 Out<br>of 242<br>(42%) | 98<br>Out of<br>242<br>(42%) | 98 Out of<br>242<br>(42%) | 98 Out of<br>242<br>(42%) |

| Delay(ns)                 | 15.386                    | 10.731                       | 10.112                    | 7.714                     |

| Power<br>consumption(%mw) | 17                        | 16                           | 16                        | 6                         |

#### **V. CONCLUSION**

In this paper, a static CMOS CSKA structure called "HYBRID CSKA" was proposed, which exhibits a lower power consumption and lower design area and high speed compared with the conventional one. The high speed and low area and energy efficient can be achieved by using the hybrid mux for the skip logic in the proposed method. The simulation results suggested that the CSKA structure is a useful adder for the applications where the speed and energy consumption and area are critical.

## REFERENCES

[1] I. Koren, *Computer Arithmetic Algorithms*, 2nd ed. Natick, MA, USA: A K Peters, Ltd., 2002.

[2] R. Zlatanovici, S. Kao, and B. Nikolic, "Energy– delay optimization of 64-bit carry-lookahead adders with a 240 ps 90 nm CMOS design example," *IEEE J. Solid-State Circuits*, vol. 44, no. 2, pp. 569–583, Feb. 2009.

[3] S. K. Mathew, M. A. Anders, B. Bloechel, T. Nguyen, R. K. Krishnamurthy, and S. Borkar, "A 4-GHz 300-mW 64-bit integer execution ALU with dual supply voltages in 90-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 40, no. 1, pp. 44–51, Jan. 2005..

[4] V. G. Oklobdzija, B. R. Zeydel, H. Q. Dao, S. Mathew, and R. Krishnamurthy, "Comparison of high-performance VLSI adders in the energy-delay space," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, no. 6, pp. 754–758, Jun. 2005.

[5] B. Ramkumar and H. M. Kittur, "Low-power and areaefficient carry select adder," *IEEE Trans. Very Large Scale*  Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371–375, Feb. 2012.

[6] M. Vratonjic, B. R. Zeydel, and V. G. Oklobdzija, "Lowand ultra low-power arithmetic units: Design and comparison," in *Proc. IEEE Int. Conf. Comput. Design, VLSI Comput. Process. (ICCD)*, Oct. 2005, pp. 249–252.

[7] C. Nagendra, M. J. Irwin, and R. M. Owens, "Area-timepower tradeoffs in parallel adders," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 43, no. 10, pp. 689–702, Oct. 1996.

[8] Y. He and C.-H. Chang, "A power-delay efficient hybrid carry- lookahead/carry-select based redundant binary to two's complement converter," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 1, pp. 336–346, Feb. 2008.

[9] C.-H. Chang, J. Gu, and M. Zhang, "A review of 0.18  $\mu$ m full adder performances for tree structured arithmetic circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 13, no. 6, pp. 686–695, Jun. 2005.

[10] D. Markovic, C. C. Wang, L. P. Alarcon, T.-T. Liu, and J. M. Rabaey, "Ultralow-power design in near-threshold region," *Proc. IEEE*, vol. 98,no. 2, pp. 237–252, Feb. 2010.

[11] R. G. Dreslinski, M. Wieckowski, D. Blaauw, D. Sylvester, and T. Mudge, "Near-threshold computing: Reclaiming Moore's law through energy efficient integrated circuits," *Proc. IEEE*, vol. 98, no. 2, pp. 253–266, Feb. 2010.

[12] S. Jain *et al.*, "A 280 mV-to-1.2 V wide-operatingrange IA-32 processor in 32 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers (ISSCC)*, Feb. 2012, pp. 66–68.

[13] R. Zimmermann, "Binary adder architectures for cellbased VLSI and their synthesis," Ph.D. dissertation, Dept. Inf. Technol. Elect. Eng., Swiss Federal Inst. Technol. (ETH), Zürich, Switzerland, 1998.

[14] D. Harris, "A taxonomy of parallel prefix networks," in *Proc. IEEE Conf. Rec. 37th Asilomar Conf. Signals, Syst., Comput.*, vol. 2. Nov. 2003, pp. 2213–2217.

[15] P. M. Kogge and H. S. Stone, "A parallel algorithm for the efficient solution of a general class of recurrence equations," *IEEE Trans. Comput.*, vol. C-22, no. 8, pp. 786– 793, Aug. 1973.

[16] V. G. Oklobdzija, B. R. Zeydel, H. Dao, S. Mathew, and R. Krishnamurthy, "Energy-delay estimation technique for high- performance microprocessor VLSI adders," in *Proc. 16th IEEE Symp. Comput. Arithmetic*, Jun. 2003, pp. 272–279.

[17] M. Lehman and N. Burla, "Skip techniques for highspeed carry- propagation in binary arithmetic units," *IRE Trans. Electron. Comput.*, vol. EC-10, no. 4, pp. 691–698, Dec. 1961.

[18] K. Chirca *et al.*, "A static low-power, high-performance 32-bit carry skip adder," in *Proc. Euromicro Symp. Digit. Syst. Design (DSD)*, Aug./Sep. 2004, pp. 615–619.

[19] M. Alioto and G. Palumbo, "A simple strategy for optimized design of one-level carry-skip adders," *IEEE Trans. Circuits Syst. 1, Fundam. Theory Appl.*, vol. 50, no. 1, pp. 141–148, Jan. 2003.

[20] S. Majerski, "On determination of optimal distributions of carry skips in adders," *IEEE Trans. Electron. Comput.*, vol. EC-16, no. 1, pp. 45–58, Feb. 1967.

[21] A. Guyot, B. Hochet, and J.-M. Muller, "A way to build efficient carry- skip adders," *IEEE Trans. Comput.*, vol. C-36, no. 10, pp. 1144–1152, Oct. 1987.

[22] S. Turrini, "Optimal group distribution in carry-skip adders," in *Proc. 9th IEEE Symp. Comput. Arithmetic*, Sep. 1989, pp. 96–103.

[23] P. K. Chan, M. D. F. Schlag, C. D. Thomborson, and V. G. Oklobdzija, "Delay optimization of carry-skip adders and block carry-lookahead adders using multidimensional dynamic programming," *IEEE Trans. Comput.*, vol. 41, no. 8, pp. 920–930, Aug. 1992.

[24] V. Kantabutra, "Designing optimum one-level carryskip adders," *IEEE Trans. Comput.*, vol. 42, no. 6, pp. 759– 764, Jun. 1993. [25] V. Kantabutra, "Accelerated two-level carry-skip adders—A type of very fast adders," *IEEE Trans. Comput.*, vol. 42, no. 11, pp. 1389–1393, Nov. 1993.

[26] S. Jia *et al.*, "Static CMOS implementation of logarithmic skip adder," in *Proc. IEEE Conf. Electron Devices Solid-State Circuits*, Dec. 2003, pp. 509–512.

[27] H. Suzuki, W. Jeong, and K. Roy, "Low power adder with adaptive supply voltage," in *Proc. 21st Int. Conf. Comput. Design*, Oct. 2003, pp.

[28] H. Suzuki, W. Jeong, and K. Roy, "Low-power carryselect adder using adaptive supply voltage based on input vector patterns," in *Proc. Int. Symp. Low Power Electron. Design (ISLPED)*, Aug. 2004, pp. 313–318.

[29] Y. Chen, H. Li, K. Roy, and C.-K. Koh, "Cascaded carry-select adder (C2 SA): A new structure for low-power CSA design," in *Proc. Int. Symp. Low Power Electron. Design (ISLPED)*, Aug. 2005, pp. 115–118.

[30] Y. Chen, H. Li, J. Li, and C.-K. Koh, "Variable-latency adder (VL-adder): New arithmetic circuit design practice to overcome NBTI," in *Proc. ACM/IEEE Int. Symp. Low Power Electron. Design (ISLPED)*, Aug. 2007, pp. 195–200.