# International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE) Vol 5, Issue 3, March 2018

## Implementation of Interleave Division Multiple Access (IDMA) and comparison using different sources in Wireless Communication System

[1] Abhishek Kumar Srivastava, [2] Pratyush Tripathi

[1] Student, [2] Assitant Professor

Department of Electronics and Communication, Kanpur Institute of Technology, Kanpur

Abstract: - This paper provides a review on the IDMA (Interleave Division Multiple Access) technology in wireless communication system based on Interleaver. In this paper, IDMA technique is proposed in AWGN channel. IDMA is a multi- user scheme in which chip Interleavers are the only means of user separation. The IDMA performance in terms of bit error rate, error rate is discussed. Here comparision with different sources is done on the basis of error rate and various different parameters.

Keywords: - Additive White Gaussian Noise (AWGN), Interleave Division Multiple Access (IDMA), PSK, Gold sequence generator, Kasami sequence generator.

#### I. INTRODUCTION

From last several years, the broadband communication service in wireless grows rapidly. It gains extensive popularity in all over the world. Due to various parameters in wireless communication systems, it also performs many personal or organizational requirements. It include mobility and cost effectiveness that need the transmission of high rate data are highly reliable in order to fulfill the increasing services applications such as high quality audio recording, messaging services, and video chatting in next generation mobile system that is 4G generation. Existing wireless technologies reliably cannot support high rates of data, because of these technology fading become very sensitive. For broadband wireless networks, the various multiple access technique (MA) has been proposed to support multiservice transmissions over the shared wireless link. In wireless communication system, the multiple access technique is one of the most efficient methods, particularly used in cellular network by mobile phone communication system. In recent that is many years back, the availability in wireless networks can be exceeded by the use of bandwidth. It has been studied that, various techniques are used to make the efficiency of bandwidth utilization; is better more users can be allotted in the cell. So that it can provide sufficient space within each cell. Previously existed multi- access techniques like FDMA, TDMA and CDMA are used in 1G/2G/3G systems are suitable for voice communication only but it is not suitable for burst data traffic and high data rate transmission which would be the

dominant part in 4G system for traffic load. For high mobility, the data rate is up to 100 Mega bits per second (Mbps) and for low mobility the data rate is up to 1 Giga bits per sec (Gbps). But the 3rd generation systems allows the data rate of nearly 3.6 to 7.2 Mbps. usually if the systems fulfill all these requirements then it can be considered as fourth generation (4G) systems. There are different types of multiple approaching techniques which are proposed for 4G systems follows CDMA, MC- CDMA, OFDMA and IDMA. In code division multiple access, every user assigned a single coded sequence and it is used to encode the significance of information signal. The receiver knows the sequence of the user code. After reception, it converts or decodes the received signal and retrieves the sequence of data. Hence the spectrum of the coded sequence is selected to be larger than the information signal. In Multi-carrier CDMA, it is also a multiple access technique which is used in orthogonal frequency division multiplexing based telecommunication system. It permits the system to hold multiple-users at identical time. Multicarrier CDMA system is highly complex in receiver and exceedingly necessary for changing the spreaded code at high data rates in transmitter which build the system inefficient. One of the most multi-carrier techniques that are used in modulation system that transmits the signal through multiple carriers is nothing but orthogonal frequency division multiplexing (OFDM). These sub carriers are orthogonal to each other and they have different frequencies. On the other side, the orthogonal frequency division multiplexing is quickly detect or response the slight changes

### International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE)

**Vol 5, Issue 3, March 2018**

in carrier or offset frequency and phase noise than compared to single carrier systems. OFDM subcarriers result in the appearance of inter-carrier interference (ICI) and common phase error (CPE) due to loss of orthogonality in OFDM. To maintain the condition of orthogonality and to eliminate the loss of collision between the Interleavers in the channel. In OFDM, the cyclic prefix needs to be greater than the time delay increases in the channel.

A basic fundamental of Interleave division multiple access i.e. IDMA is differentiated by two users in Interleaver. A multi- user technique in which chip Interleaved are only means of separating the users that is nothing but IDMA. The iterative multi-user detection is done by receiver in chip-by-chip form. In this work, by combining the OFDM and IDMA, we propose a new method referred as a multi-user system in the mobile radio environment.

All users can transmit their information in same time at same frequency band in OFDM and IDMA method. By using Interleaving technique, the orthogonality can be obtained between the users. The choice of good Interleaver must demonstrate that the inter leavers are weekly correlated, do not require large memory or large bandwidth to communicate between transmitter and receiver and easy to generate.

#### II. IDMA MECHANISM

In wireless communication system, Interleaving can be referred as a technique which is commonly used to overcome noise in the channel such as error burst or fading. In Interleaving process, the input data bits reorder itself such that consecutive bits of data are exchanged and splitted among various blocks in a known pattern among them. At receiver, the Interleaved data is arranged back to original sequence of bits with the help of de-interleaver. As a result, introducing the correlated noise in transmission channel seems to be statistically independent at the receiver in interleaving and thus allocate better error correction.

In IDMA system, there exist several areas which are still open for the researchers. Many of them includes the optimum design of integral parts of IDMA communication system and hence future applications of IDMA mechanism in other areas including satellite communication, LAN networking, optical communications, power line communications, MIMO system and UWB technologies. In addition to this its horizon are still open for investigation about optimum modulation, channel coding, spreading, interleaving, and detection techniques.

The IDMA can be performed in terms of bit error rate and compare its complexity with an Inter-symbol interference cancellation technique for AWGN multipath channel. Thus, it promises a better performance that is compared with OFDM and IDMA when the existing information is

completely evaluated. However we noticed that during iterative process the OFDM and IDMA out performs the IDMA with ISI Cancellation when numbers of users are increased. Indeed, increasing the number of users in MAI and ISI is carried out in IDMA requires independent processing.

#### **Interleavers in IDMA Scheme**

In [2], the Interleavers based on multi-access method has discussed earlier for large bandwidth efficiency, performance is improved and receiver complexity is low. This method depends on interleaving as the only mean to differentiate the signal from particular users. Then it is named as interleave division multiple access (IDMA). The user-specific Interleavers play a vital function in IDMA system. In case of turbo codes and decoding, the decorrelation between adjacent bit sequence is not possible. The correlation between the Interleavers should compute, the signals that get affected strongly from other user and the decoding process of specific user also get effected [1]. The transmitter and receiver doesn't store or communicate maximum bits in order to agree with interleaving sequence. It might be demonstrated that defining the correlation between the Interleavers .It can be used to produce the collision criteria, where zero cross- correlation implies that, it is not collided. In IDMA systems, transmission is required for transfer the matrix Interleaver. Whereas in receiver, it consist of spreaded data along with the interleaving pattern and is related to the users. So that larger the size of the Interleavers, more bandwidth are consumed during transmission, more the orthogonality is achieved among interleaver [1].

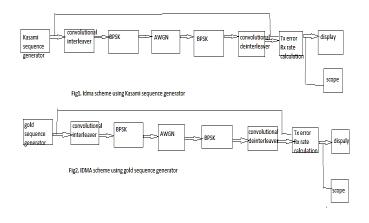

### Schematic diagram of IDMA Scheme using different sources

Fig 3 Schematic diagram of IDMA

## International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE)

**Vol 5, Issue 3, March 2018**

In fig1.Kasami sequence generator is used as source. Convolutional interleaver are used then binary phase shift keying modulator then AWGN channel is used. It is passed through **BPSK** demodulator and convolutional deinterleaver is used. Then error rate calculator calculates the error between transmitter and receiver. In fig2.Gold sequence generator is used as source. Convolutional interleaver are used then binary phase shift keying modulator then AWGN channel is used. It is passed convolutional through **BPSK** demodulator and deinterleaver is used. Then error rate calculator calculates the error between transmitter and receiver

#### **Gold Sequence Generator**

#### Generate Gold sequence from set of sequences

The Gold Sequence Generator block generates a Gold sequence. Gold sequences form a large class of sequences that have good periodic cross-correlation properties.

#### **Kasami Sequence Generator**

Generate Kasami sequence from set of Kasami sequences. The Kasami Sequence Generator block generates a sequence from the set of Kasami sequences. The Kasami sequences are a set of sequences that have good cross-correlation properties.

#### **Convolutional Interleaver**

Permute input symbols using set of shift registers. The Convolutional Interleaver block permutes the symbols in the input signal. Internally, it uses a set of shift registers. The delay value of the kth shift register is (k-1) times the Register length step parameter. The number of shift registers is the value of the Rows of shift registers parameter.

#### **PSK Modulator**

Modulate using Phase frequency shift keying method. The PSK Modulator Baseband block modulates using the Phase frequency shift keying method. The output is a baseband representation of the modulated signal.

#### **AWGN Channel**

Add white Gaussian noise to input signal. The AWGN Channel block adds white Gaussian noise to a real or complex input signal. When the input signal is real, this block adds real Gaussian noise and produces a real output signal. When the input signal is complex, this block adds complex Gaussian noise and produces a complex output signal. This block inherits its sample time from the input signal.

#### PSK Demodulator

Demodulate PSK-modulated data. The PSK Demodulator Baseband block demodulates a signal that was modulated using the Phase frequency shift keying method. The input is a baseband representation of the modulated signal. The input and output for this block are discrete-time signals.

The input can be either a scalar or a frame-based column vector of type single or double.

#### **Convolutional Deinterleaver**

Restore ordering of symbols that were permuted using shift registers. The Convolutional Deinterleaver block recovers a signal that was interleaved using the Convolutional Interleaver block. The parameters in the two blocks should have the same values.

#### **Error Rate Calculator**

Compute bit error rate or symbol error rate of input data. The Error Rate Calculation block compares input data from a transmitter with input data from a receiver. It calculates the error rate as a running statistic, by dividing the total number of unequal pairs of data elements by the total number of input data elements from one source.[12]

#### SIMULATION RESULTS

| Parameter        | Kasami         | Gold sequence  |

|------------------|----------------|----------------|

|                  | sequence       | generator with |

|                  | generator with | convolutional  |

|                  | convolutional  | interleaver    |

|                  | interleaver    |                |

| Target no. of    | 100            | 100            |

| errors           |                | A Charles      |

| Max. no. of      | 1e5            | 1e5            |

| symbols          |                |                |

| Error rate       | 0.4505         | 0.5051         |

| Total no. of     | 100            | 100            |

| errors           |                |                |

| The total no. of | 222            | 198            |

| comparisons      |                |                |

| 0.5    |

|--------|

| 89     |

| double |

| 1/1200 |

|        |

|        |

| 0.5    |

| 89     |

| double |

|        |

|        |

| 1/1200 |

| 6      |

| 2      |

| 0      |

|        |

| 0      |

|        |

### International Journal of Engineering Research in Electronics and Communication Engineering (IJERECE)

Vol 5, Issue 3, March 2018

| Data type  Awgn channel  Initial seed 67  Eb/No(dB) 10  No. of bits per symbol 1  Signal power (watts) 1  Symbol period 1  PSK demodulation  Phase offset 0  Decision type Hard type  Convolutional deinterleaver  Sample time 1/1200  Row of shift register 6  Register length step 2  Initial condition 0  Error rate display  Computational delay 0  Receive delay 0  Display  Format short  decimation 1                                          |                        |           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|

| Initial seed 67  Eb/No(dB) 10  No. of bits per symbol 1  Signal power (watts) 1  Symbol period 1  PSK demodulation  Phase offset 0  Decision type Hard type  Convolutional deinterleaver  Sample time 1/1200  Row of shift register 6  Register length step 2  Initial condition 0  Error rate display  Computational delay 0  Receive delay 0  Display  Format short                                                                                 | Data type              | double    |

| Eb/No(dB) 10 No. of bits per symbol 1 Signal power (watts) 1 Symbol period 1 PSK demodulation Phase offset 0 Decision type Hard type Convolutional deinterleaver Sample time 1/1200 Row of shift register 6 Register length step 2 Initial condition 0 Error rate display Computational delay Receive delay 0 Display Format short                                                                                                                    | Awgn channel           |           |

| No. of bits per symbol Signal power (watts) Symbol period PSK demodulation Phase offset Decision type Hard type Convolutional deinterleaver Sample time Register length step Initial condition O Error rate display Computational delay Receive delay Display Format  1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                             | Initial seed           | 67        |

| Signal power (watts)  Symbol period  PSK demodulation  Phase offset  Decision type  Convolutional deinterleaver  Sample time  Row of shift register  Register length step  Initial condition  Error rate display  Computational delay  Receive delay  Display  Format  I 1 200  1 1 200  1 1 200  1 1 200  1 1 200  1 2 2 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3                                                                                           | Eb/No(dB)              | 10        |

| Symbol period  PSK demodulation  Phase offset  Decision type  Convolutional deinterleaver  Sample time  Row of shift register  Register length step  Initial condition  Error rate display  Computational delay  Receive delay  Display  Format  O  Display  1  Display  Display  Display  Interval demodulation  Display  Analysis of the demodulation  Display  Analysis of the demodulation  Display  Analysis of the demodulation  Display  Short | No. of bits per symbol | 1         |

| PSK demodulation Phase offset 0 Decision type Hard type  Convolutional deinterleaver Sample time 1/1200 Row of shift register 6 Register length step 2 Initial condition 0 Error rate display Computational delay 0 Receive delay 0 Display Format short                                                                                                                                                                                              | Signal power (watts)   | 1         |

| Phase offset 0 Decision type Hard type  Convolutional deinterleaver Sample time 1/1200 Row of shift register 6 Register length step 2 Initial condition 0 Error rate display Computational delay 0 Receive delay 0 Display Format short                                                                                                                                                                                                               | Symbol period          | 1         |

| Decision type  Convolutional deinterleaver  Sample time  Row of shift register  Register length step  Initial condition  Error rate display  Computational delay  Receive delay  Display  Format  Hard type  1/1200  0  1/1200  Register length step 2  Initial condition 0  Unitial condition 0  Error rate display  Short                                              | PSK demodulation       |           |

| Convolutional deinterleaver  Sample time 1/1200  Row of shift register 6  Register length step 2  Initial condition 0  Error rate display  Computational delay 0  Receive delay 0  Display  Format short                                                                                                                                                                                                                                              | Phase offset           | 0         |

| deinterleaver1/1200Sample time1/1200Row of shift register6Register length step2Initial condition0Error rate displayComputational delayComputational delay0Receive delay0DisplayFormatshort                                                                                                                                                                                                                                                            | Decision type          | Hard type |

| Sample time 1/1200 Row of shift register 6 Register length step 2 Initial condition 0 Error rate display Computational delay 0 Receive delay 0 Display Format short                                                                                                                                                                                                                                                                                   | Convolutional          |           |

| Row of shift register Register length step 2 Initial condition 0 Error rate display Computational delay 0 Receive delay 0 Display Format short                                                                                                                                                                                                                                                                                                        | deinterleaver          |           |

| Register length step 2 Initial condition 0 Error rate display Computational delay 0 Receive delay 0 Display Format short                                                                                                                                                                                                                                                                                                                              | Sample time            | 1/1200    |

| Initial condition 0  Error rate display  Computational delay 0  Receive delay 0  Display  Format short                                                                                                                                                                                                                                                                                                                                                | Row of shift register  | 6         |

| Error rate display  Computational delay 0  Receive delay 0  Display  Format short                                                                                                                                                                                                                                                                                                                                                                     | Register length step   | 2         |

| Computational delay 0 Receive delay 0 Display Format short                                                                                                                                                                                                                                                                                                                                                                                            | Initial condition      | 0         |

| Receive delay 0 Display Format short                                                                                                                                                                                                                                                                                                                                                                                                                  | Error rate display     |           |

| Display Format short                                                                                                                                                                                                                                                                                                                                                                                                                                  | Computational delay    | 0         |

| Format short                                                                                                                                                                                                                                                                                                                                                                                                                                          | Receive delay          | 0         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Display                |           |

| decimation 1                                                                                                                                                                                                                                                                                                                                                                                                                                          | Format                 | short     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                       | decimation             | 1         |

#### III. CONCLUSION

We have outlined the basic principles of IDMA and the simulation results with the help of AWGN channel. We have calculated the error rate by error rate calculator and found error rate of Kasami sequence generator with convolutional interleaver is lower than gold sequence generator with convolutional interleaver. Based on the implementation of IDMA we found that Kasami sequence generator with convolutional interleaver is better than gold sequence generator with convolutional interleaver.

#### REFERENCES

- [1] L.Ping, L. Liu, K. Wu, and W.K. Leung, "Interleave-Division Multiple-Access," IEEE Trans. Wireless Commun., Vol.5, No. 4, pp.938-947, Apr.2006.

- [2] P.Wang, J. Xiao, and L. Ping, "Comparison of orthogonal and non-orthogonal approaches to future wireless cellular systems," IEEE Veh. Technol. Mag., vol.1, no. 3, pp.4-11, Sept.2006.

- [3] Peter Hammarberg and Fredrik Rusek. "Channel Estimation algorithm for OFDM-IDMA: complexity and performance", IEEE Transactions on wireless communication, vol.-11, pp.1723-1734, no.5, may 2012.

- [4] Ruchir Gupta, B.K. Kanauji a, R.C.S. Chauhan, M.ShuklaMember IEEE, "Prime Interleaver for Multiuser Iterative IDMA Systems" in International Conference on Computational Intelligence and Communication Network, DOI 10.1109/CICN.2010.119.

- [5] B.Muquet and M.De.Couville, "Blind and Semi-Blind Channel identification methods using second order statistics for OFDM transmission" IEEE Transaction on signal processing, pp.2745-8, Mar.1993.

- [6] H.liu and G.Xu, "A deterministic approach to blindestimation," IEEE signal processing letters, vol.1, no.12, pp.205-7, Dec.1994.

- [7] M.Shukla, V.K.Srivastava, S.Tiwari "Interleave Division MultipleAccessforWirelessCommunication":ICONGENCO M-06

- [8] Kuldeep choudhary, P.S Sharma "Interleavers for IDMA Technology: A Comparison Survey": IJARCCE Vol.1, Issue 2, Apr 2012.

- [9] Aashish Shukla, DhirajPurwar, Dileep Kumar "Multiple Access Schemes for (4G) Communication: A Comparison Survey": ISDMISC (IJCA) 2011.

- [10] Li Ping and Peng Wang, Xiaodong Wang "Recent Progress in Interleave-Division Multiple-Access (IDMA)".

- [11] Farheen Begum "Implementation of Interleave Division Multiple Access (IDMA) with Multiple Users in Wireless Communication System", International Journal of Computer Applications (0975 8887) Volume 134 No.15, January 2016

- [12] Matalb Tool (help)